### CS 220

#### The MIPS Instruction Pipeline – Part 2

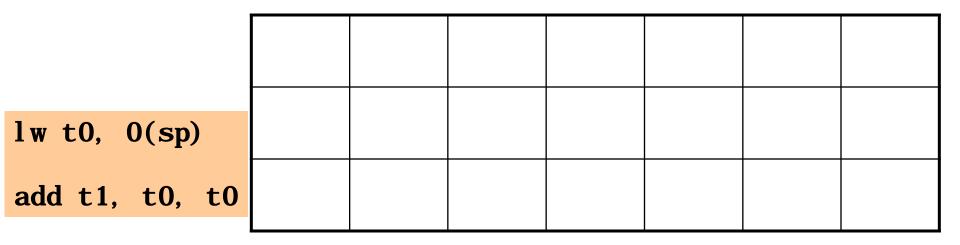

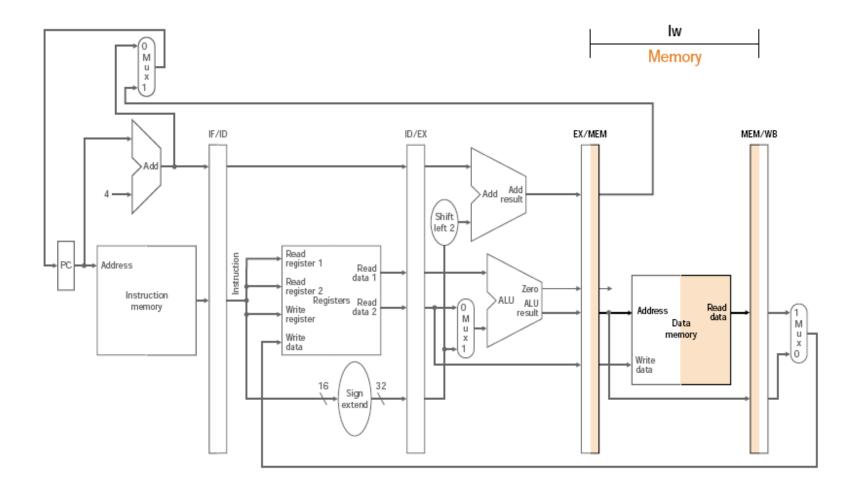

## Reading memory

Analyze a data dependency with a **Iw** instruction.

Solutions?

### Can we minimize stalling?

Assuming these variables are stored in memory write the MIPS code for these statements.

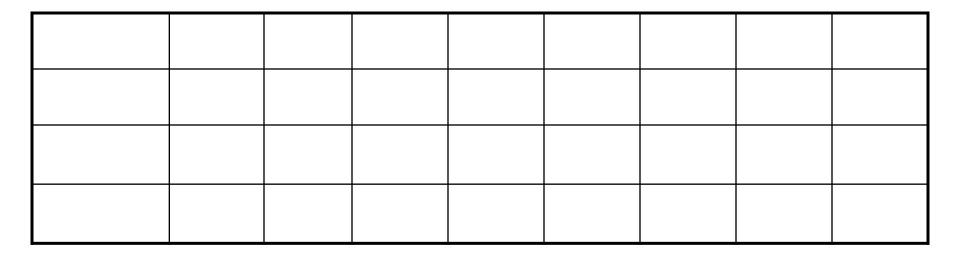

#### Control Hazard: MIPS Solution

loop: addi \$t0, \$t0, -1 bne \$t0, \$zero, loop ori \$v0, \$zero, 9 add \$t3, \$t4, \$t5

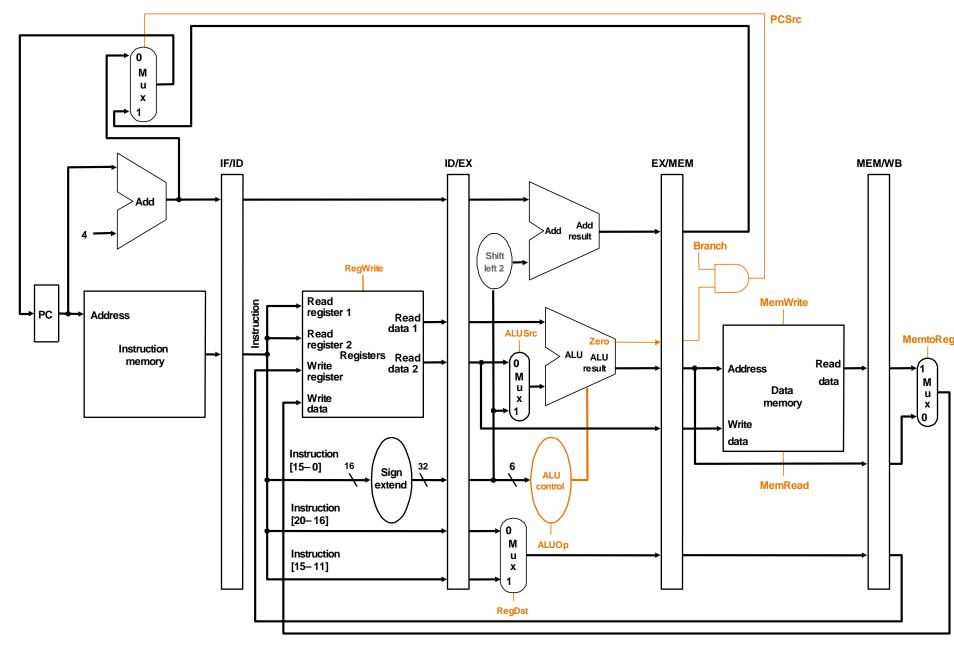

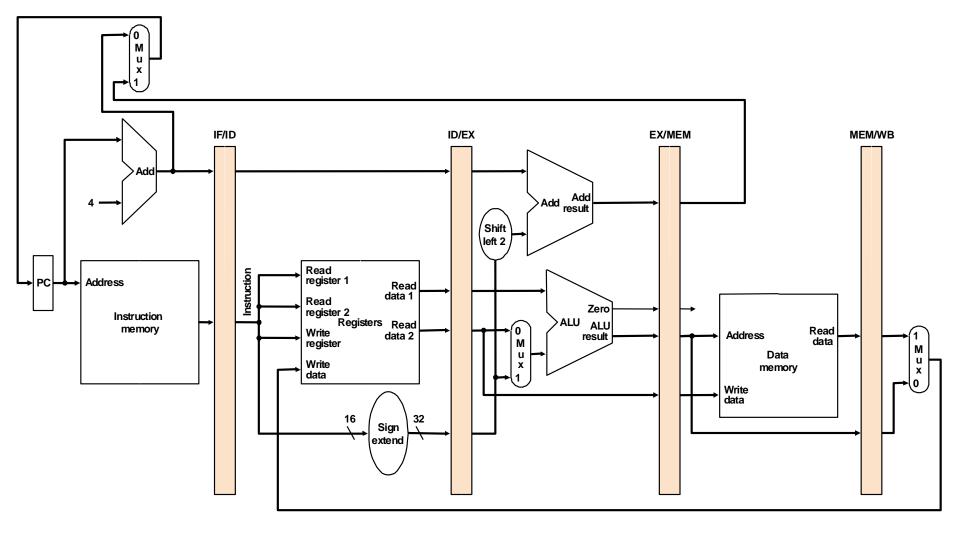

# **Pipelined Datapath**

## **Pipelined Datapath**

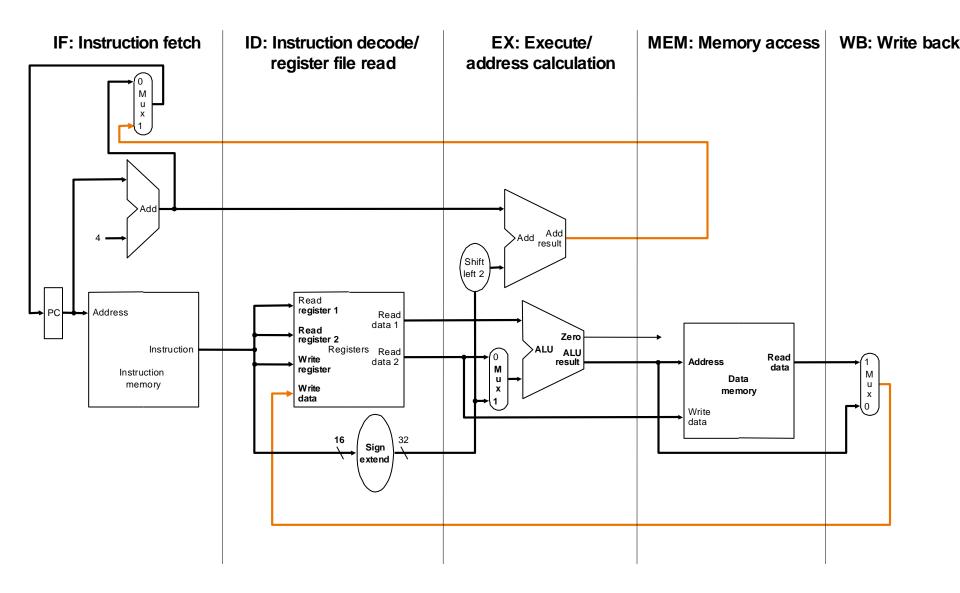

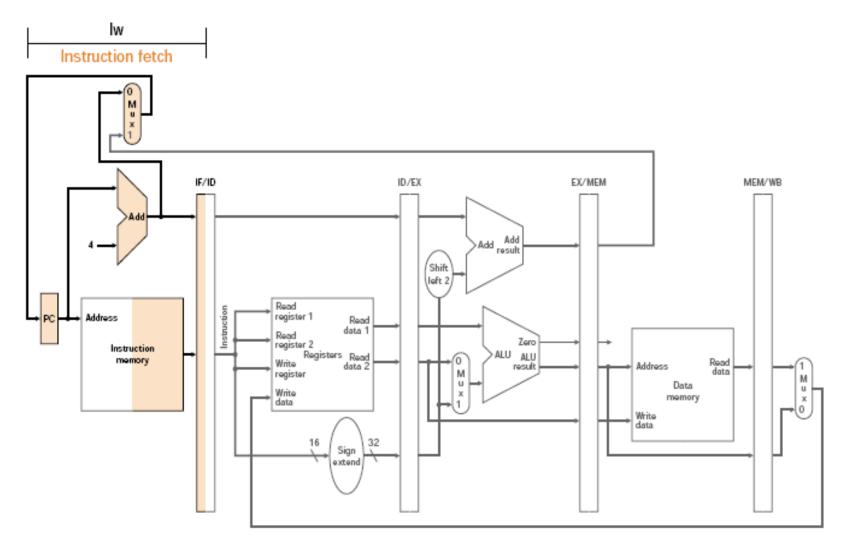

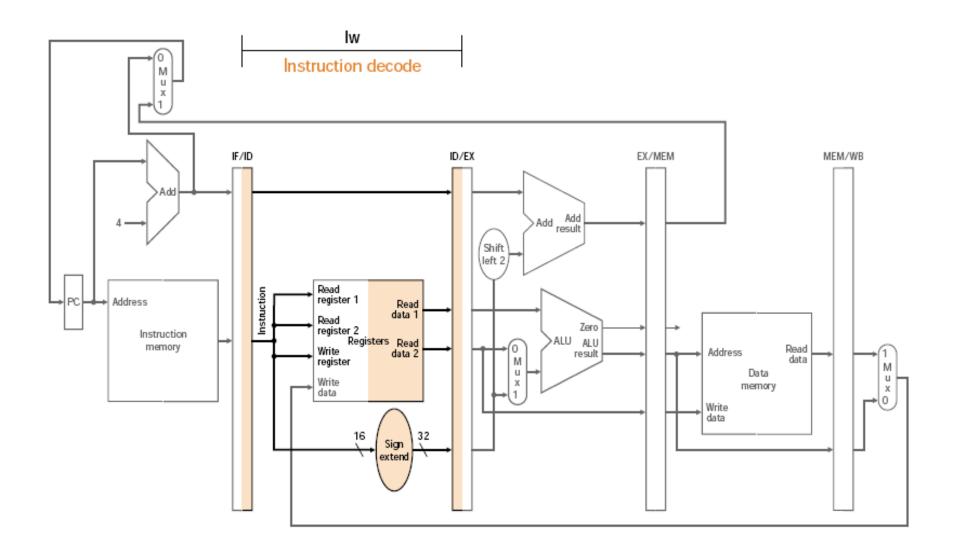

### Tracing a LW instruction

### Tracing a LW instruction

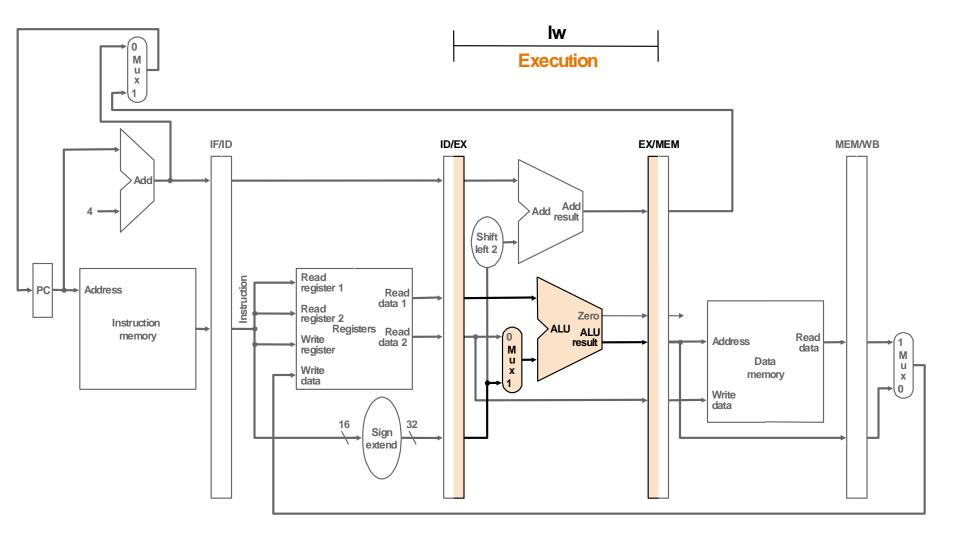

# Tracing LW: EX

# LW: Memory

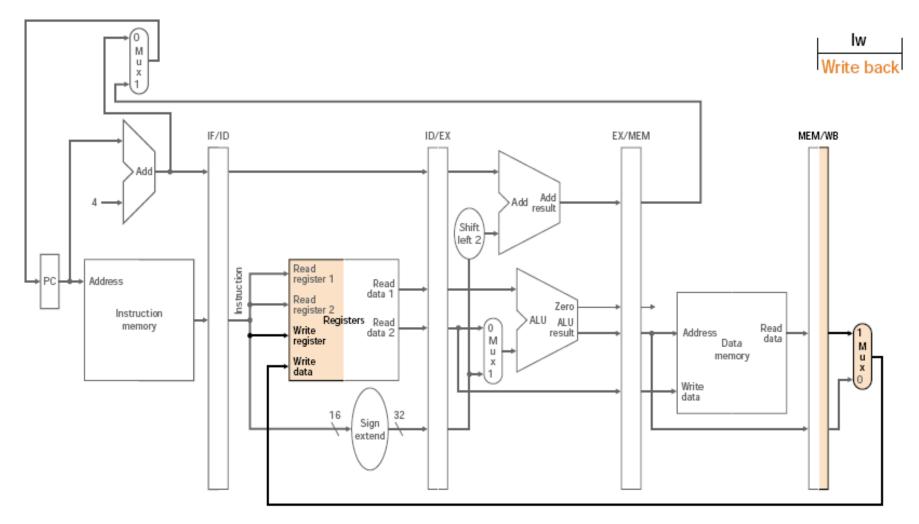

### LW: Writeback

Problem?

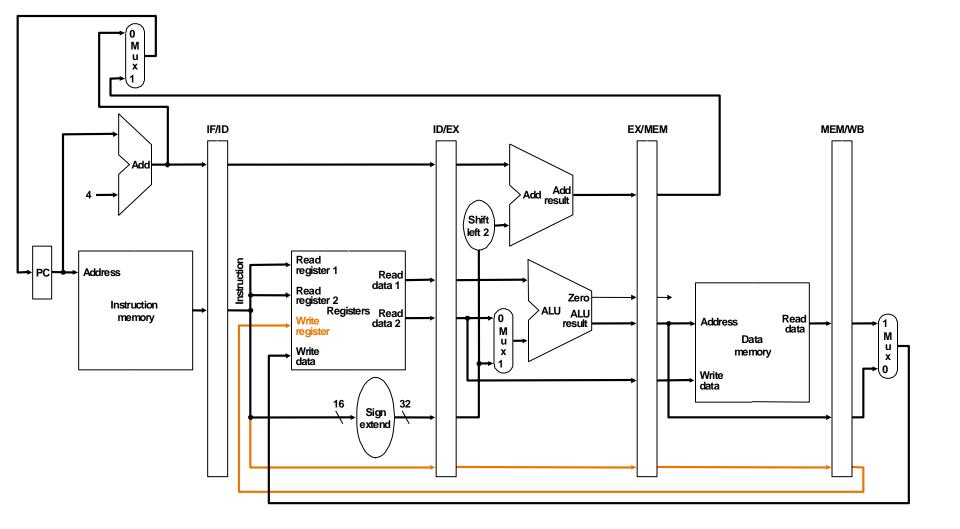

### Iw Writeback: bug fixed

#### Pipelined Datapath w/Control Signals