#### Abstract

HARCOURT, EDWIN ALAN. Formal Specification of Instruction Set Processors and the Derivation of Instruction Schedulers. (Under the Direction of Jon Mauney and Thomas K. Miller, III.)

We present two techniques for formally specifying an instruction set processor at the *pro*grammer's view — the architecture view and the timing view. From the timing specification we show how to derive an instruction scheduler for the processor.

One technique addresses architecture specification, that is, the information required to write correct programs. At the architectural level we present a functional semantics that captures the property that instructions are functions from processor state to processor state.

The second specification technique addresses the programmer's view of the timing of the processor, that is, the needed information required to write temporally efficient programs. We present a technique for formally describing, at a *high-level*, the timing properties of pipelined, superscalar processors. We illustrate the technique by specifying and simulating a hypothetical processor that includes many features of commercial processors including delayed loads and branches, interlocked floating-point instructions, and multiple instruction issue. As our mathematical formalism we use SCCS, a synchronous process algebra designed for specifying timed, concurrent systems. Putting our specification to use, we show how to construct an instruction-scheduler from the specification by deriving appropriate parameters needed for instruction scheduling. These parameters include instruction latencies, illegal instruction combinations, resource constraints, and instructions that may be issued in parallel.

### The Formal Specification of Instruction Set Processors and the Derivation of Instruction Schedulers

by Edwin Alan Harcourt

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

**Computer Science**

Raleigh

1994

Approved by:

Co-chair of Advisory Committee

Co-chair of Advisory Committee

#### Biography

Edwin A. Harcourt received a B.S. in Computer Science from the State University of New York at Plattsburgh in 1986. In 1989 he received an M.S. in Computer Engineering (1989) and in 1994 a Ph.D. in Computer Science both from North Carolina State University.

# Contents

|   | List        | of Figures                                      | viii     |  |  |  |  |  |  |  |

|---|-------------|-------------------------------------------------|----------|--|--|--|--|--|--|--|

| 1 | Intr        | coduction                                       | 1        |  |  |  |  |  |  |  |

|   | 1.1         | The Architecture Level                          | <b>2</b> |  |  |  |  |  |  |  |

|   | 1.2         | Organization Detail vs. Timing Detail           | 3        |  |  |  |  |  |  |  |

|   | 1.3         | Static Instruction Scheduling                   | 4        |  |  |  |  |  |  |  |

|   | 1.4         | Outline of Dissertation                         | 4        |  |  |  |  |  |  |  |

| 2 | Mat         | athematical Specifications and Related Research |          |  |  |  |  |  |  |  |

|   | 2.1         | Hardware Description Languages                  | 6        |  |  |  |  |  |  |  |

|   | 2.2         | Formal Specification Languages                  | 9        |  |  |  |  |  |  |  |

|   |             | 2.2.1 Sequential Formalisms                     | 9        |  |  |  |  |  |  |  |

|   |             | 2.2.2 Formalisms of Concurrency and Time        | 12       |  |  |  |  |  |  |  |

|   | 2.3         | Compiler Code Generator Generation Languages    | 14       |  |  |  |  |  |  |  |

|   |             | 2.3.1 Resource Requirements                     | 15       |  |  |  |  |  |  |  |

|   |             | 2.3.2 A Marion Extension                        | 17       |  |  |  |  |  |  |  |

|   |             | 2.3.3 Other Processor Features                  | 18       |  |  |  |  |  |  |  |

|   | 2.4         | Summary — The Specification Language Zoo        | 18       |  |  |  |  |  |  |  |

| 3 | Fun         | tional ISA Specification 21                     |          |  |  |  |  |  |  |  |

|   | <b>3</b> .1 | Denotational Semantics                          | 21       |  |  |  |  |  |  |  |

|   | 3.2         | Semantic Algebras                               | 22       |  |  |  |  |  |  |  |

|   | 3.3         | The Semantics of ISA's                          | 23       |  |  |  |  |  |  |  |

|   |      | 3.3.1 Notation                                      | 23 |

|---|------|-----------------------------------------------------|----|

|   |      | 3.3.2 The Syntactic Domain                          | 24 |

|   |      | 3.3.3 The Semantic Actions                          | 24 |

|   |      | 3.3.4 The Valuation Function                        | 27 |

|   | 3.4  | Action Implementation                               | 33 |

|   | 3.5  | Code Generation                                     | 34 |

|   | 3.6  | Discussion                                          | 35 |

| 4 | Trad | truction Timing                                     | 36 |

| 4 |      | -                                                   |    |

|   | 4.1  | Architecture and Organization                       | 36 |

|   | 4.2  | Delayed Instructions                                | 37 |

|   | 4.3  | Multicycle Instructions                             | 38 |

|   | 4.4  | Resource Constraints                                | 38 |

|   | 4.5  | Multiple Instruction Issue                          | 38 |

|   | 4.6  | Motivation                                          | 39 |

|   | 4.7  | Functions Don't Work                                | 39 |

| 5 | sco  | CS: A Synchronous Calculus of Communicating Systems | 41 |

|   | 5.1  |                                                     | 41 |

|   | 5.2  | -                                                   | 42 |

|   | 5.3  |                                                     | 42 |

|   | 5.4  | -                                                   | 44 |

|   | 5.5  | Extensions to SCCS                                  | 45 |

|   | 5.6  | Transition Graphs                                   | 46 |

|   | 5.7  | The Operational Semantics of SCCS                   | 47 |

|   | 5.8  | Examples                                            | 50 |

|   |      | 5.8.1 A Zero-Delay and a Unit-Delay Wire            | 50 |

|   |      | 5.8.2 Logic Gates                                   | 50 |

|   |      | 5.8.3 Flip-Flop                                     | 51 |

| Spe  | cifying a Processor                                                                                                                                                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1  | Our example microprocessor                                                                                                                                                                         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.2  | Timing Constraints                                                                                                                                                                                 | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3  | The SCCS Specification                                                                                                                                                                             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4  | Instruction Formats as Actions                                                                                                                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.5  | Defining the Registers                                                                                                                                                                             | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.5.1 Register Locking                                                                                                                                                                             | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.6  | Defining Memory                                                                                                                                                                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.7  | Instruction Pipeline                                                                                                                                                                               | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.8  | Instruction Issue                                                                                                                                                                                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.8.1 Arithmetic Instructions                                                                                                                                                                      | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.8.2 Integer Load and Store Instructions                                                                                                                                                          | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.8.3 The Branch Instruction                                                                                                                                                                       | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.9  | Interlocked Floating-Point Instructions                                                                                                                                                            | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.9.1 Floating-Point Registers                                                                                                                                                                     | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.9.2 The Fadd instruction                                                                                                                                                                         | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.10 | Structural Constraints                                                                                                                                                                             | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.10.1 Modeling Finite Resources                                                                                                                                                                   | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.10.2 Multi-cycle Floating-point Instructions                                                                                                                                                     | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.11 | A Normal Form                                                                                                                                                                                      | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.11.1 Register Locking                                                                                                                                                                            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.11.2 Resource Requirements                                                                                                                                                                       | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 6.11.3 Undefined Instruction Sequences                                                                                                                                                             | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.12 | Summary                                                                                                                                                                                            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Mul  | ltiple Instruction-Issue Processors                                                                                                                                                                | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.1  | An $Integer 	imes Float$ Superscalar $\ldots \ldots \ldots$                                                                  | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 7.1.1 Instruction Issue                                                                                                                                                                            | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.2  | An $Integer 	imes Integer$ Superscalar $\dots \dots \dots$                                         | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 7.2.1 Data Dependencies (or Data Hazards)                                                                                                                                                          | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 7.2.2 Specifying Data Hazards                                                                                                                                                                      | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> <li>6.12</li> <li>Mu</li> <li>7.1</li> </ul> | <ul> <li>6.2 Timing Constraints.</li> <li>6.3 The SCCS Specification</li> <li>6.4 Instruction Formats as Actions</li> <li>6.5 Defining the Registers</li> <li>6.5.1 Register Locking</li> <li>6.6 Defining Memory</li> <li>6.7 Instruction Pipeline</li> <li>6.8 Instruction Pipeline</li> <li>6.8.1 Arithmetic Instructions</li> <li>6.8.2 Integer Load and Store Instructions</li> <li>6.8.3 The Branch Instruction</li> <li>6.9 Interlocked Floating-Point Instructions</li> <li>6.9.1 Floating-Point Registers</li> <li>6.9.2 The Fadd instruction</li> <li>6.10.1 Modeling Finite Resources</li> <li>6.10.2 Multi-cycle Floating-point Instructions</li> <li>6.11.1 Register Locking</li> <li>6.11.2 Resource Requirements</li> <li>6.11.3 Undefined Instruction Sequences</li> <li>6.12 Summary</li> <li>7.1 An Integer × Float Superscalar</li> <li>7.2.1 Data Dependencies (or Data Hazards)</li> <li>7.2 Na Maticipe Superscalar</li> <li>7.2.1 Data Dependencies (or Data Hazards)</li> </ul> |

#### v

|                                        | 7.3  | An $Integer 	imes Integer 	imes Float$ Superscalar | 77  |  |  |  |  |  |  |  |  |  |

|----------------------------------------|------|----------------------------------------------------|-----|--|--|--|--|--|--|--|--|--|

| 8                                      | Sim  | imulation 79                                       |     |  |  |  |  |  |  |  |  |  |

|                                        | 8.1  | 1 The Reactive View                                |     |  |  |  |  |  |  |  |  |  |

|                                        | 8.2  | Simulation                                         | 80  |  |  |  |  |  |  |  |  |  |

|                                        | 8.3  |                                                    |     |  |  |  |  |  |  |  |  |  |

|                                        | 8.4  |                                                    |     |  |  |  |  |  |  |  |  |  |

|                                        | 8.5  | Example: A Floating-Point Vector Sum               | 81  |  |  |  |  |  |  |  |  |  |

| 9                                      | Inst | ruction Scheduling                                 | 85  |  |  |  |  |  |  |  |  |  |

| -                                      | 9.1  | Instruction Scheduling                             | 85  |  |  |  |  |  |  |  |  |  |

|                                        | 0.1  | 9.1.1 Constraints                                  | 86  |  |  |  |  |  |  |  |  |  |

|                                        |      | 9.1.2 Instruction Scheduling Algorithms            | 87  |  |  |  |  |  |  |  |  |  |

|                                        |      |                                                    |     |  |  |  |  |  |  |  |  |  |

| 10                                     |      | iving Instruction Scheduling Parameters            | 92  |  |  |  |  |  |  |  |  |  |

|                                        | 10.1 | Preliminaries                                      | 92  |  |  |  |  |  |  |  |  |  |

|                                        | 10.2 | Derivation of Scheduling Parameters                | 93  |  |  |  |  |  |  |  |  |  |

|                                        |      | 10.2.1 The Algorithm                               | 94  |  |  |  |  |  |  |  |  |  |

|                                        | 10.3 | Determining Illegal Instruction Sequences          | 99  |  |  |  |  |  |  |  |  |  |

|                                        |      | 10.3.1 A Modal Logic for SCCS                      | 99  |  |  |  |  |  |  |  |  |  |

|                                        |      | 10.3.2 Using the logic in a processor              | 101 |  |  |  |  |  |  |  |  |  |

|                                        | 10.4 | Determining Possible Multiple-Issue Instructions   | 103 |  |  |  |  |  |  |  |  |  |

|                                        | 10.5 | Computing the Resource Usage Functions             | 105 |  |  |  |  |  |  |  |  |  |

|                                        |      | 10.5.1 Particulate Actions and Agent Sorts         | 105 |  |  |  |  |  |  |  |  |  |

|                                        |      | 10.5.2 Resources and Actions                       | 106 |  |  |  |  |  |  |  |  |  |

|                                        |      | 10.5.3 Deriving the Resource Usage Functions       | 106 |  |  |  |  |  |  |  |  |  |

|                                        | 10.6 | Summary                                            | 109 |  |  |  |  |  |  |  |  |  |

| 11 Conclusions and Future Research 111 |      |                                                    |     |  |  |  |  |  |  |  |  |  |

|                                        | 11.1 | Programmer's Timing View                           | 111 |  |  |  |  |  |  |  |  |  |

|                                        |      | 11.1.1 Instruction Scheduling                      | 112 |  |  |  |  |  |  |  |  |  |

|                                        | 11.2 | Future Research                                    | 112 |  |  |  |  |  |  |  |  |  |

|              |             | 11.2.1 Interrupts                            | 12  |

|--------------|-------------|----------------------------------------------|-----|

|              |             | 11.2.2 Cache Model                           | 13  |

|              |             | 11.2.3 Verification and Synthesis            | 13  |

|              | 11.3        | Formal Methods                               | 15  |

| $\mathbf{A}$ | Exa         | mple circuits in the Concurrency Workbench 1 | 16  |

|              | <b>A.</b> 1 | Simple Logic Gates                           | 17  |

|              |             | A.1.1 Not Gates                              | 18  |

|              | A.2         | Half-Adder                                   | 18  |

|              |             | A.2.1 Specification                          | 18  |

|              |             | A.2.2 Implementation                         | 19  |

|              | A.3         | Wires                                        | 20  |

|              | A.4         | Full-Adder                                   | 22  |

|              |             | A.4.1 Specification                          | 22  |

|              |             | A.4.2 Implementation                         | 23  |

|              | A.5         | Flip-Flop                                    | 24  |

|              |             | A.5.1 Implementation                         | 24  |

|              |             | A.5.2 Specification                          | 25  |

| в            | Our         | example RISC in the Concurrency Workbench 1  | 27  |

|              | <b>B</b> .1 | The CWB Listing                              | .27 |

# List of Figures

| 2.1         | A VHDL description of an inverter.                                | 8          |

|-------------|-------------------------------------------------------------------|------------|

| 2.2         | A full-adder specified in SML.                                    | 10         |

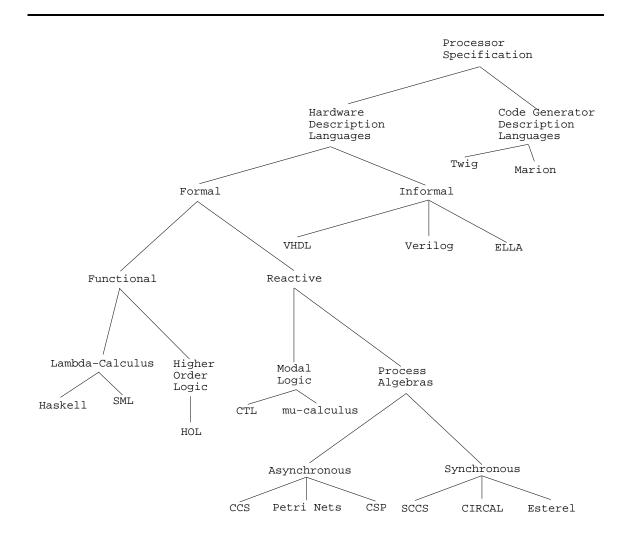

| 2.3         | The classification of specification languages.                    | 19         |

| <b>3</b> .1 | Syntactic domain that specifies PDP-11 instruction formats        | <b>25</b>  |

| 3.2         | Syntax of semantic actions that specify RTL.                      | 26         |

| 3.3         | The Semantics of the PDP-11 Addressing Modes                      | 29         |

| <b>3</b> .4 | Semantics of PDP-11 Instructions.                                 | 30         |

| <b>3.5</b>  | Semantics of PDP-11 Instructions (continued).                     | <b>3</b> 1 |

| 3.6         | Semantics of PDP-11 Instructions (continued).                     | 32         |

| 3.7         | RTL Syntax tree corresponding to the instruction Add R1, (R2)+    | 35         |

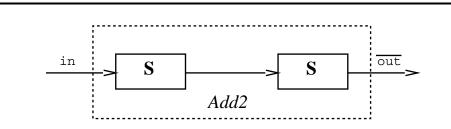

| 5.1         | A two stage "Add 2" pipeline constructed from two "Add 1" agents. | 41         |

| 5.2         | Syntax of SCCS expressions                                        | 43         |

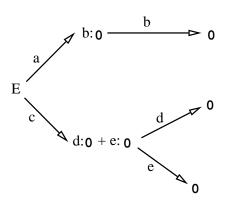

| 5.3         | Transition graph of agent defined in Equation 5.4.                | 47         |

| 5.4         | Operational semantics of SCCS.                                    | 48         |

| 5.5         | Equational laws of SCCS                                           | 49         |

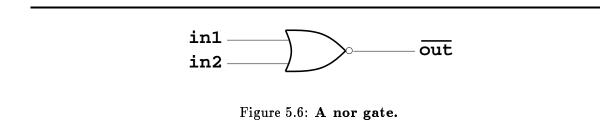

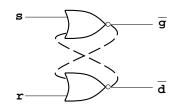

| 5.6         | <b>A</b> nor gate                                                 | 52         |

| 5.7         | A flip-flop constructed from two nor-gates (Figure 5.6)           | 52         |

| 6.1         | RISC instruction set.                                             | 54         |

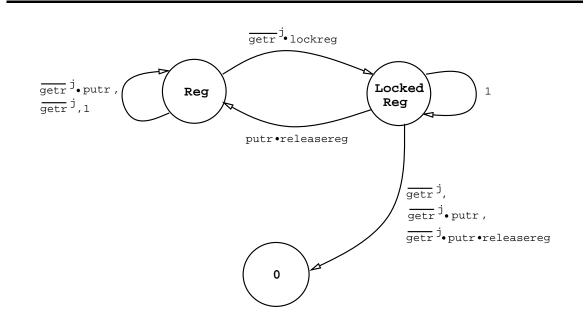

| 6.2         | State transition graph of agent <i>Reg</i> in Equation 6.8        | 59         |

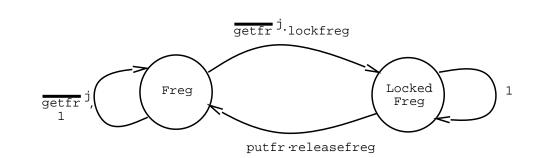

| 6.3         | State transition graph of a floating-point register, Freg         | 65         |

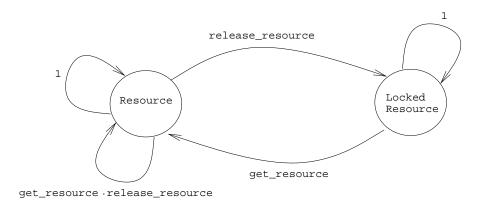

| 6.4         | State transition graph of a <i>Resource</i> in Equation 6.25.     | 68         |

| 7.1  | Possible data dependencies in instruction sequences.               | 76  |

|------|--------------------------------------------------------------------|-----|

| 7.2  | Possible three-issue instruction sequences.                        | 78  |

| 8.1  | Derivation of program executing on the processor.                  | 80  |

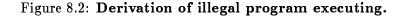

| 8.2  | Derivation of illegal program executing.                           | 82  |

| 8.3  | Program that calculates a vector sum                               | 82  |

| 8.4  | Transition graph of vector sum from Figure 8.3                     | 83  |

| 9.1  | Dependency graph of vector sum program from Figure 8.3             | 87  |

| 9.2  | Part of resource usage function for $MIPS/R4000$ FDIV instruction. | 88  |

| 9.3  | Generic list scheduling algorithm.                                 | 90  |

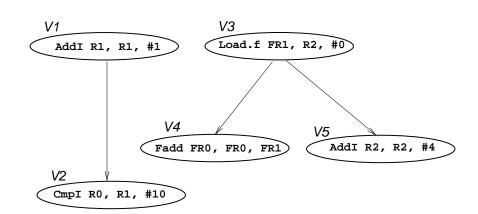

| 9.4  | The structure of a typical compiler.                               | 91  |

| 10.1 | Algorithm that derives instruction latencies.                      | 97  |

| 10.2 | Algorithm to detect illegal instruction pairs.                     | 102 |

| 10.3 | Algorithm to detect multiple instruction issue pairs               | 104 |

| 10.4 | Algorithm to calculate resource usage functions.                   | 107 |

### Chapter 1

## Introduction

A specification of a system is a precise description of the desired behavior of the system which any implementation should provide. Specifications have traditionally been expressed in natural language which, unfortunately, can be vague and hence lead to imprecision and ambiguity. To remedy this problem many specifications are now being expressed *formally* (*i.e.*, using some mathematical framework such as first-order logic or algebraic techniques). Once a formal specification has been written, several tasks can be performed: the specification may be used to help derive an implementation, construct a simulator for the system, or aid in writing documentation.

This dissertation addresses the problem of specifying an instruction set processor in a way that is useful for building compilers. An *instruction set processor* is what we normally think of as a microprocessor or CPU. Specifically, we address formally specifying a processor at two levels: the architecture level and the instruction timing level. Also, we show how a timing specification can be used to derive an instruction scheduler for the processor.

Formal processor specifications are valuable for a variety of reasons.

- Formal specifications aid in the design process. They require the user to thoughtfully plan and design the system.

- Processor verification requires a formal specification in order to carry out proofs of correctness.

- If the specification language is executable (and both SML and SCCS are) then a timing level simulator is *automatically* available.

- High-level synthesis (whether compilers or hardware) requires some form of a specification.

- Formal specifications are used for precise documentation.

Instruction set processors are best viewed hierarchically at various levels of abstraction. A common partitioning of the hierarchy is as follows:

- The *instruction set architecture* (or just architecture) level is a functional view that represents the processor as seen by the assembly language programmer (or compiler writer). This view only includes information needed to write functionally correct programs.

- The organization level includes the general structure of the processor in terms of functional units which include include integer and floating point pipelines, branch units, caches, buses, internal latches, etc.

- The logic level contains the low level implementation details of the functional units.

When discussing or making an argument about a processor one has to be clear about the level of abstraction at issue. The user of a processor is usually concerned with the architectural level, since the user must have this information to write correct programs.

#### 1.1 The Architecture Level

At its highest level, an architecture is an *abstract data type* where memory and registers (i.e., the machine state) constitute the data and the machine instructions are the operations defined on the data. At this level, instructions are essentially functions that map states to states. Usually, a simple *register transfer language*, or RTL, notation suffices to describe the computational effect(s) of an instruction. For example, the instruction

Add  $R_i$ ,  $R_j$ ,  $R_k$

may be described by the register transfer statement

Reg[i] := Reg[j] + Reg[k].

Until recently, there has been no language available for specifying processors at the architectural level. Cook [29] remedied this by designing a language specifically for designing instruction sets. Since the architecture level provides a functional view, where instructions are functions from processor state to processor state, it can be formalized using a functional

language. In Chapter 3 we present a functional semantics of a processor at the architecture level using the language SML [78].

#### 1.2 Organization Detail vs. Timing Detail

Besides writing correct programs, a user would also like to write efficient programs. Hence, the user needs more information than is contained in an architecture specification. For example, in some RISC architectures the following instruction sequence is not the most efficient.

| (1) | Load | R1, | (R2) | )  | ;R1 | := | Men | 1 [ F | <b>1</b> 2] |

|-----|------|-----|------|----|-----|----|-----|-------|-------------|

| (2) | Add  | R2, | R2,  | R1 | ;R2 | := | R2  | +     | R1          |

| (3) | Add  | R3, | R3,  | #1 | ;R3 | := | R3  | +     | 1           |

Instruction (2) will usually cause an interlock (because (2) needs to wait for R1 to be loaded from memory by (1)), which wastes cycles and causes the pipeline to stall. On some processors the sequence is illegal which causes the value of R1 to be undefined during instructions (1) and (2). However, instructions (2) and (3) may be switched without altering the meaning of the program, and this switch would reduce the number of stall cycles or make the sequence valid.

When one instruction can interact with another and alter the computational effect in undefined ways (e.g., the load instruction above) or when we wish to capture timing information so that we can write efficient programs, then viewing instructions as functions is no longer sufficient. We consider this point further in Chapter 2.

In many modern instruction set processors, the temporal and concurrent properties of the instructions are visible to the user of the processor. Consequently, such properties should be included in a behavioral processor specification. We present a technique for formally describing, at a *high-level*, the timing properties of pipelined, superscalar processors [76, 55]. We illustrate the technique by specifying and simulating a hypothetical processor that includes many features of commercial processors including delayed loads and branches, interlocked floating-point instructions, and multiple instruction issue (superscalar). As our mathematical formalism we use SCCS (Synchronous Calculus of Communication Systems), a synchronous process algebra designed for specifying timed, concurrent systems [68, 67]. After showing how to specify a processor we parameterize the instruction scheduling problem and demonstrate how to derive these scheduling parameters from the specification, essentially yielding an instruction scheduler for the architecture.

#### **1.3 Static Instruction Scheduling**

Once a processor has been defined at the instruction timing level there are several ways in which the specification can be used. A hardware designer could use the specification as the *requirements specification* that any implementation must meet.

However, a particular level of abstraction is both a *specification* of a lower level and an *implementation* of a higher level. For example, the organization level can be viewed as an implementation of the architecture level and as a specification for the logic level. In a similar vein our timing specification could also be viewed as an implementation of the processor for a higher level, the compiler level. It is in this way that we use our timing specification: by extracting scheduling information from the timing specification and putting it in a form suitable for use with an "off the shelf" instruction scheduler.

A subsequent goal of this research, then, is to utilize our specification by generating instruction scheduling information (e.g., latencies, resource requirements) directly from the specification. We develop algorithms that analyze SCCS descriptions and yield the instruction scheduling information. The algorithms depend on the formal operational semantics of SCCS, which is defined in terms of an abstract machine known as a *labeled transition system*.

#### **1.4 Outline of Dissertation**

The rest of this dissertation is organized as follows:

- There have been a variety of methods used to specify low-level digital hardware, both formal and informal. Chapter 2 reviews this related research and further motivates our choice of using the synchronous process algebra, SCCS.

- Instructions at the highest level are, mathematically, state transformation functions. Chapter 3 gives a functional semantics to an example architecture, using the functional language SML.

- In Chapter 4 we motivate the need for expressing programmer level timing constraints in processor specifications.

- In Chapter 5 we introduce SCCS both formally (using structural operational semantics) and informally (with several examples of using SCCS to describe some simple combinational and sequential circuits).

- Chapter 6 formally specifies, using SCCS, the instructions and the their timing constraints of a hypothetical, yet realistic, RISC style processor.

- Chapter 7 shows how we can use SCCS to specify various Superscalar configurations of our example architecture.

- The operational semantics of SCCS maps SCCS programs to abstract machines. Our SCCS specification is, therefore, executable, in terms of the abstract machine it represents. In Chapter 8 we discuss how the behavior of our architecture is simulated.

- Chapter 9 gives a brief introduction to instruction scheduling and sets the stage for deriving instruction scheduling information from the SCCS specification.

- Chapter 10 describes how to derive instruction scheduling parameters, including instruction latencies, resource constraints, illegal instruction sequences (e.g., delayed loads) and multiple instruction issue.

- Chapter 11 concludes and discusses future research.

- For purposes of introducing SCCS with some simple examples, Appendix A gives the SCCS implementation (using the Concurrency Workbench) of some simple digital circuits.

- Appendix B gives an SCCS implementation of our example RISC architecture using the Concurrency Workbench.

### Chapter 2

# Mathematical Specifications and Related Research

At first, researchers hoped that there might exist some one unique ideal specification language. But what could it be? Perhaps some kind of logic, say full first order logic? Or perhaps Horn clause logic? Or equational logic? Or LCF? What about the lambda calculus? Or perhaps we should take a state transition approach ...? But none of these seemed to work.

(Joseph Goguen - One, None, a Hundred Thousand Specification Languages)

There are many formalisms available and currently being applied for specifying the intended behavior and/or semantics of computer hardware and architectures. In this chapter we review hardware description languages (e.g., Verilog and VHDL) [65, 3, 29, 5, 6, 40], formal specification languages such as first-order logic [18], higher-order logic [47, 11, 91, 9, 61, 10], temporal logic [80, 94, 43], equational algebra [90, 42, 39], relational algebra [85], concurrency formalisms [53, 67, 68, 69, 66, 17, 34, 44, 8, 16, 83], the Z specification language [13, 12, 87], type theory [54, 48], and the lambda calculus [45, 46, 88, 75, 21]. We also review compiler code generator generators which also provide specification languages for describing processors [1, 37, 33, 81, 15].

#### 2.1 Hardware Description Languages

The term "hardware description language" (or HDL) is not a well-defined term. Traditionally it means "any language used to specify hardware". But this definition is too broad as this would include imperative programming languages such as C, Pascal, and Ada and abstract formalisms such as Constructive Type Theory [54] and Category Theory [85]. Usually an HDL refers to languages such as VHDL and Verilog which are imperative style programming languages extended with primitives and libraries that aid in describing hardware.

There are a variety of HDL's such as Verilog [92], VHDL [62], ISPS [5], and ELLA [72]. All of them suffer in that they lack a formal definition. HDL's are extensions of imperative programming languages and their problems can be traced to the problems of imperative languages — such as aliasing and side-effects. It has also been suggested that HDL's be abandoned altogether and that imperative programming languages be used. Using Ada as an HDL has been addressed in [6, 40]. Also, while HDL's are useful for simulating low-level digital hardware they are unsuitable for use in high-level processor specification as pointed out by Cook [29].

VHDL is one of the more popular hardware description languages [62]; Figure 2.1 shows the VHDL code that describes the behavior of a simple inverter. There is nothing too surprising about this description other than that it is a lot of code for specifying a simple inverter. A more serious problem, however, is that, since VHDL is not formally defined, attempting to ascertain the behavior of even simple circuits (let alone more complicated circuits) is dependent upon individual implementations of VHDL. For example, the keyword, **transport** in the inverter specification specifies that the delay in the **after** clause corresponds to the propagation delay associated with passing a value through a wire. If the keyword **transport** is omitted then delay corresponds, not to a propagation delay in a wire, but to the "hold time", that is, the amount of time the signal must persist in order for it to be considered as a signal. Other timing complications are introduced by the various forms of the **wait** statement on processes – **wait**, **wait on**, **wait for**, **wait until**, **wait** *time-expression*.

Another criticism frequently leveled at VHDL is that the timing primitives of VHDL are low-level and overly concrete as the programmer is required to specify timing constraints in nanoseconds or femtoseconds (one femtosecond is the smallest unit of time in VHDL). If one wishes to view time more abstractly in terms of, say, clock cycles then a "clock process" must be constructed that models a clock and every process must then perform their actions based on a signal that this clock process emits. These same criticisms apply to Verilog, the other most widely used HDL, as it is similar to VHDL.

```

- Define some enumeration types.

type Logic is ('0','1');

type Delay_flag is (Zero_delay,Const_delay);

- The interface to the inverter.

entity INV is

generic (Time_flag: Delay_flag);

port (X: in Logic; Y: out Logic);

end INV;

- Specify the behavior of the inverter.

architecture Behavior of INV is

begin

p0: process

variable delay: Time := 0 Ns;

begin

if Time_flag = Const_delay then delay := 0.83 Ns;

end if;

if X = '0', then

Y <= transport '1' after delay;

else

Y <= transport '0' after delay;

end if;

wait on X;

end process;

end Behavior;

```

Figure 2.1: A VHDL description of an inverter.

#### 2.2 Formal Specification Languages

A formal specification language is one that is based on some rigorous mathematical framework. The specification then becomes amenable to analysis using the mathematical tools of the framework. For example, if we specify a system using first-order logic we may then be able to use resolution to perform proofs about the system.

Formal specification languages fall into two broad categories: *functional* (or relational) and *reactive*. A *functional* view of a system is one that maps an initial state to a final state. (Or in the relational view, mapping an input to a *set* of outputs). This view is appropriate for programs that accept all of their inputs when the program begins executing and yields its output when the program terminates [80]. For example, a compiler maps source programs to target programs.

Some systems have no final output and termination is viewed as a catastrophe rather than as a virtue. The behavior of these *reactive* systems is defined in terms of the ongoing interaction with their environment. For example, an operating system should not terminate and has no final output but has an ongoing interaction with users to service their requests. Any concurrent system can be viewed as reactive because, even if its overall role is functional, the system is composed of interacting components [80]. It is in this way that we view a microprocessor: reactively as a system of interacting components (instructions, registers, and functional units).

A recent overview of formal methods applied to the design and analysis of digital systems can be found in [90].

#### 2.2.1 Sequential Formalisms

We use the term *sequential* to mean a formalism that does not include primitives to specify concurrency or time. Sequential formalisms include functional languages (based on the  $\lambda$ -calculus), algebraic theories, first-order logic, and higher-order logic.

#### **Functional Specification**

There has been some research into specifying hardware and architectures using functional methods. Paillet [75] presents a functional semantics of a CISC-style microprocessor at the instruction set level. No attempt was made to specify instruction timing properties or instruction interaction; rather the intent of the research was to use the specification as a basis to verify an implementation, although this was not done.

```

fun HalfAdder(a,b) = (a <> b, a andalso b)

fun FullAdder(Cin, a, b) =

let

val (Sum'', Carry') = HalfAdder(a,b)

val (Sum', Carry') = HalfAdder(Cin,Sum'')

in

(Sum', Carry' orelse Carry'')

end

```

Figure 2.2: A full-adder specified in SML.

Charlton [21] presents a technique of introducing a clock into a functional specification by using "lazy lists" to represent an infinite stream of clock pulses. The research was limited to a consideration of how one could introduce a clock in a functional model; nothing was subsequently done with the specification.

Gordon [45, 46] represents finite-state systems using the  $\lambda$ -calculus. He then showed how one could verify circuits in the  $\lambda$ -calculus using *fixpoint induction*. As an example, Figure 2.2 uses the functional language SML to specify a full-adder from two half-adders.

Of the various abstraction levels of a processor the functional view is appropriate if we wish to view it at its highest level — the architecture. In this view, instructions are functions from states to states. However, a function that represents an instruction specifies *final values* of an instruction and not how this value was computed nor how long it took to compute. This view makes it difficult to specify timing or instruction interaction.

#### HOL — Higher-Order Logic

Probably the most widely used formalism for formally specifying hardware is *higher-order logic*; in particular, the logic embodied in the HOL system of Gordon. (See Gordon [47] for an introduction to HOL and Melham [64] for using HOL in hardware verification.) Higher Order Logic is an extension of first-order logic in which variables can range over functions and predicates. HOL uses the lambda calculus to specify functions and, consequently, subsumes functional methods.

HOL is very expressive and has been used to describe other formalisms such as a subset of VHDL [11], CCS [68] (the asynchronous version of SCCS), the  $\pi$ -calculus[70] (higher order CCS), and Hoare's CSP [53]. This suggests that HOL is a good meta-language and is useful for defining other formalisms within HOL. However, there is a sense in which HOL is too expressive, according to Goguen [42]:

"most logics are too expressive! We need more restricted logics ... in order to get *executable* specification languages that can be used for rapid prototyping and even efficient programming. And we certainly want to avoid specifying systems that are unimplementable because they involve uncomputable functions or relations".

Higher order logic is undecidable. That is, it is undecidable whether a statement in higher order logic is true. Consequently, the HOL system is not a theorem prover but a proof checker and provides a "support environment" for carrying out proofs in HOL by hand. Moreover, HOL can not directly be used to simulate the system being specified as there is no notion of the operational behavior of an HOL statement [90].

As in functional methods, neither time nor concurrency are primitives in the logic but are encoded. However, because of HOL's expressiveness it is somewhat easier to represent both time and concurrency than in a functional approach. For example, to represent concurrency in HOL we do not need to talk about sets of final values but simply define two events  $\alpha$ and  $\beta$  to occur in parallel if  $\alpha$  and  $\beta$  are both true at time t, that is, if  $\alpha(t) \wedge \beta(t)$  holds. So logical conjunction is used to compose two elements in parallel.

Typically, time is represented using the natural numbers (0, 1, 2, 3, ... usually abbreviated  $\omega$ ). Consider two ports, in and out. A port can be represented as a function from time to booleans.

$$\mathtt{in}, \mathtt{out} \in oldsymbol{\omega} o bool$$

We use HOL's logical operations (the standard  $\lor, \land, \forall, \exists, =$ ) to specify constraints on the port values. For example, the invariant that the value at port out at time t + 1 is the same as the value on port in at time t is specified as,

$$orall t \in \omega.(\mathtt{out}(t+1) = \mathtt{in}(t))$$

Equation 2.1 represents a one bit unit delay element where the output at time t is the same as the input at time t - 1. Equation 2.1 also specifies that, at time 0 (power up), the contents of the register is 0.

$$\textit{Reg}(\texttt{in}, \texttt{out} \in \omega \rightarrow \textit{bool}) \stackrel{\text{def}}{=} \forall t \in \omega.\texttt{out}(t) = ((t = 0) \Rightarrow 0 \mid \texttt{in}(t - 1))$$

(2.1)

The notation  $cond \Rightarrow true | false$  is a conditional expression.

Equation 2.2 "connects" two registers together creating a delay circuit that inputs a bit at time t and outputs it at time t + 2. The types of the ports in, out,  $\ell$  are omitted for readability but are functions from time to booleans as in Equation 2.1.

$$Two Regs(\texttt{in},\texttt{out}) \stackrel{\texttt{def}}{=} \forall \texttt{in}. \forall \texttt{out}. \exists \ell. (Reg(\texttt{in}, \ell) \land Reg(\ell, \texttt{out})) \tag{2.2}$$

Equation 2.2 shows how, using conjunction, two registers are instantiated in parallel. Existentially quantifying the variable  $\ell$  makes an internal connection between the two registers.

In [26] Cohn describes the Viper microprocessor using HOL. The Viper is a microcoded processor that does not include any instruction-level parallel properties. Also, in [52], Herbert discusses specifying and verifying microcoded microprocessors using HOL in general. Again, the techniques do not address instruction-level parallelism.

#### 2.2.2 Formalisms of Concurrency and Time

There are well developed formalisms for explicitly dealing with reactive systems. The most common formalisms are process algebras and modal and temporal logics.

#### **Process Calculi**

There are a variety of formalisms for specifying asynchronous and/or synchronous concurrent systems including Petri Nets [16], CCS [68, 69], SCCS [68, 67], ACP [4], CIR-CAL [66, 34], HOP [44], ESTEREL [8], the  $\pi$ -calculus [70], and CSP [53].

Process algebras have been used to give a semantics to a communications protocol language, LOTOS [17]; a parallel object oriented language, POOL [4]; a computer integrated manufacturing system [4]; to low-level digital hardware [66]; and biological ecosystems [95]. The various calculi can be divided into asynchronous and synchronous languages. The synchronous languages can be considered "more expressive" as it is typically possible to embed an asynchronous calculus within a synchronous one. For example, the asynchronous calculus CCS is definable within the synchronous calculus SCCS [67].

In an asynchronous formalism parallelism is reduced to non-determinism (or interleaving). For example, let

- $A \times B$  mean processes A and B execute in parallel;

- A + B mean non-deterministically execute either A or B;

- a.A mean execute the action a and then become the process A.

In an asynchronous formalism if the process A can do some action a and become the process A' we will write  $A \xrightarrow{a} A'$ ; the process B can do some action b and become the process B' then the process  $A \times B$  is equivalent to the process  $a.(A' \times B) + b.(A \times B')$ . That is, the process  $A \times B$  can execute A for a step or B for a step but not both at the same time (forgetting for the moment the possibility that A and B might wish to communicate).